- 您现在的位置:买卖IC网 > Sheet目录3858 > PIC18F26J50-I/ML (Microchip Technology)IC PIC MCU FLASH 64K 2V 28-QFN

PIC18F2XJXX/4XJXX FAMILY

DS39687E-page 26

2009 Microchip Technology Inc.

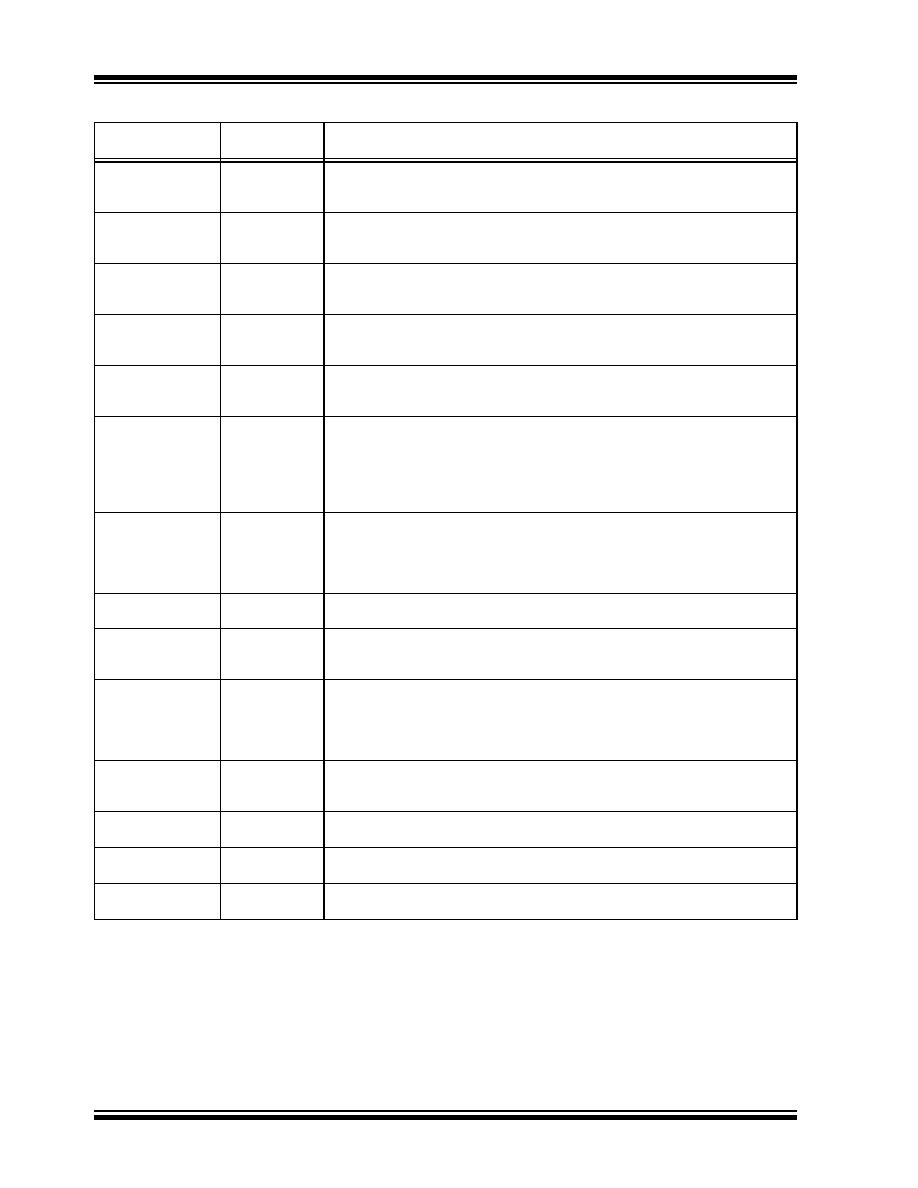

RTCOSC

CONFIG3L

RTCC Reference Clock Select bit

1 = RTCC uses T1OSC/T1CKI as reference clock

0 = RTCC uses INTRC as reference clock

DSWDTOSC

CONFIG3L

DSWDT Reference Clock Select bit

1 = DSWDT uses INTRC as reference clock

0 = DSWDT uses T1OSC/T1CKI as reference clock

CONFIG3H

MSSP 7-Bit Address Masking Mode Enable bit

1 = 7-Bit Address Masking mode enable

0 = 5-Bit Address Masking mode enable

PLLSEL(5)

CONFIG3H

PLL Selection bit

1 = 4x PLL selected

0 = 96 MHz PLL selected

ADCSEL

CONFIG3H

ADC Mode Selection bit

1 = 10-Bit ADC mode selected

0 = 12-Bit ADC mode selected

IOL1WAY

CONFIG3H

IOLOCK Bit One-Way Set Enable bit

1 = The IOLOCK bit (PPSCON<0>) can be set once, provided the unlock sequence has

been completed. Once set, the Peripheral Pin Select registers cannot be written to a

second time.

0 = The IOLOCK bit (PPSCON<0>) can be set and cleared as needed, provided the

unlock sequence has been completed

WPCFG

CONFIG4L

Write/Erase Protect Configuration Words Page bit (valid when WPDIS = 0)

1 = Configuration Words page is not erase/write-protected unless WPEND and

WPFP<6:0> settings include the Configuration Words page

0 = Configuration Words page is erase/write-protected, regardless of WPEND and

WPFP<6:0>

CONFIG4L

Write/Erase Protect Page Start/End Location bits

Used with WPEND bit to define which pages in Flash will be write/erase-protected.

WPEND

CONFIG4H

Write/Erase Protect Region Select bit (valid when WPDIS = 0)

1 = Flash pages, WPFP<6:0> to Configuration Words page, are write/erase-protected

0 = Flash pages, 0 to WPFP<6:0> are write/erase-protected

WPDIS

CONFIG4H

Write Protect Disable bit

1 = WPFP<6:0>, WPEND and WPCFG bits ignored; all Flash memory may be erased or

written

0 = WPFP<6:0>, WPEND and WPCFG bits enabled; write/erase-protect active for the

selected region(s)

LS48MHZ(3)

CONFIG4H

System Clock Selection bit

1 = System clock is expected at 48 MHz, FS/LS USB CLKEN’s divide-by is set to 8

0 = System clock is expected at 24 MHz, FS/LS USB CLKEN’s divide-by is set to 4

DEV<2:0>

DEVID1

Device ID bits

Used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number.

REV<4:0>

DEVID1

Revision ID bits

Indicate the device revision.

DEV<10:3>

DEVID2

Device ID bits

Used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

TABLE 5-7:

PIC18F47J13 AND PIC18F47J53 FAMILY DEVICES: BIT DESCRIPTIONS (CONTINUED)

Bit Name

Configuration

Words

Description

Note 1: The Configuration bits can only be programmed indirectly by programming the Flash Configuration Word.

2: The Configuration bits are reset to ‘1’ only on VDD Reset; it is reloaded with the programmed value at any device Reset.

3: These bits are not implemented in PIC18F47J13 family devices.

4: Once this bit is cleared, all the Configuration registers which reside in the last page are also protected. To disable code

protection, perform an ICSP Bulk Erase operation.

5: Not implemented on PIC18F47J53 family devices.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC33FJ64GP204-E/ML

IC DSPIC MCU/DSP 64K 44-QFN

PIC32MX130F064B-I/SP

IC MCU 32BIT 64KB FLASH 28-SPDIP

PIC18F1330-I/P

IC PIC MCU FLASH 4KX16 18DIP

ATTINY12-8PC

IC AVR MCU 1K 5V 8MHZ COM 8-DIP

ATTINY11L-2SI

IC AVR MCU 8-BIT FLSH LOW V SO-8

ATTINY11L-2SC

IC AVR MCU 8 BIT FLSH LOW V SO-8

PIC24HJ16GP304-I/PT

IC PIC MCU FLASH 16K 44TQFP

ATTINY12V-1SC

IC AVR MCU 1MHZ 1.8V SO-8

相关代理商/技术参数

PIC18F26J50-I/SO

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-I/SP

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-I/SS

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50T-I/ML

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50T-I/SO

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50T-I/SS

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J53-I/ML

功能描述:8位微控制器 -MCU 64KB 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J53-I/SO

功能描述:8位微控制器 -MCU 64KB Flash 4KB RAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT